Hdl Designer Testbench

Testbench consist of entity without any io ports design instantiated as component clock input and.

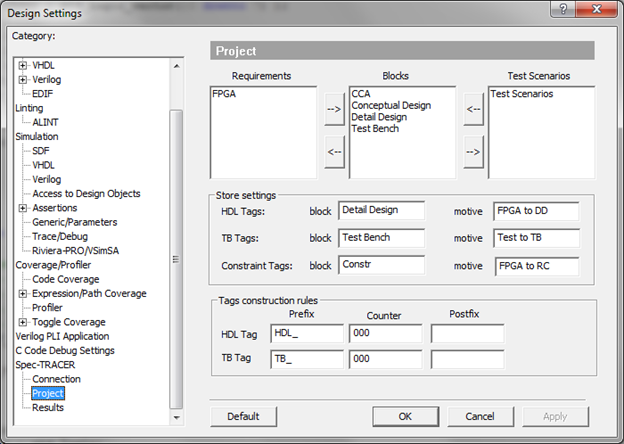

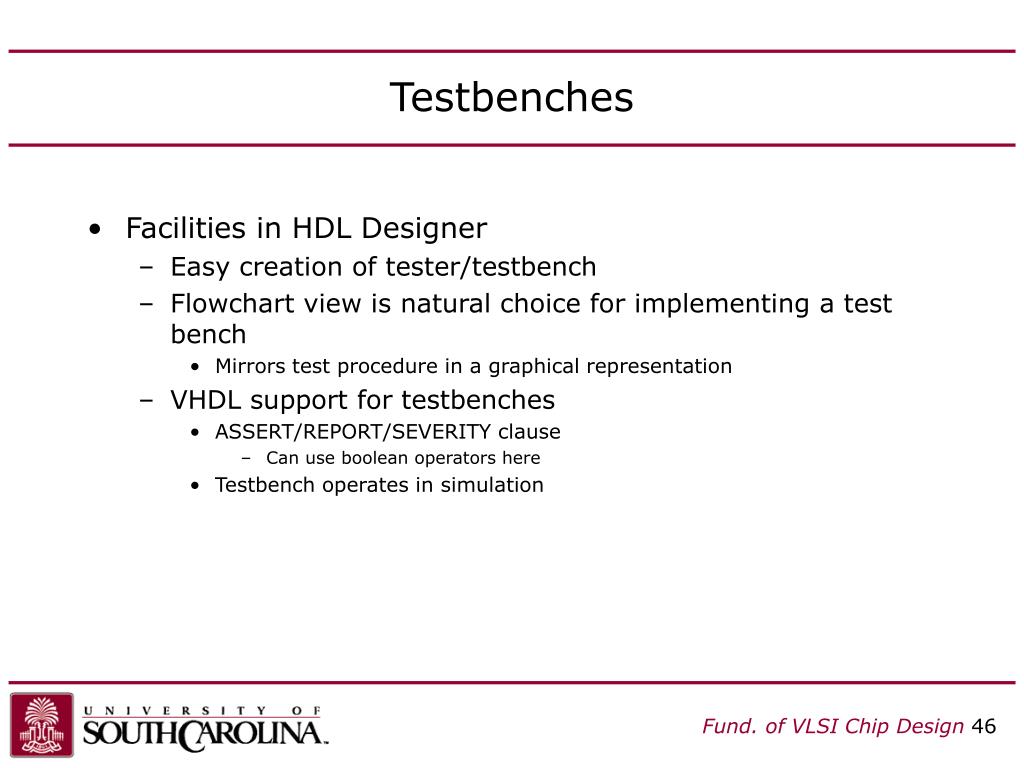

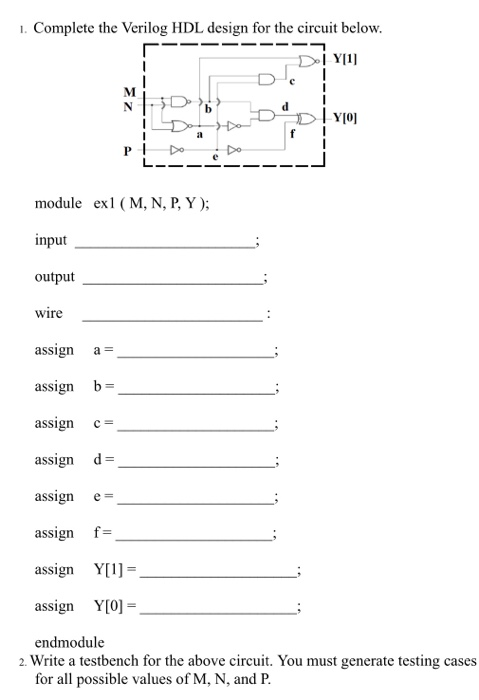

Hdl designer testbench. A multiplexer is a combinational type of digital circuits that are used to transfer one of the available input lines to the single output and which input has to be transferred to the output it will be decided by the value of the select line signal. To summarize we first design the circuit using hdl then we verify it using a testbench. In the category spec tracer project users can configure how hdl and testbench tags in active hdl will be stored in spec tracer. Prerequisite multiplexers in digital logic problem.

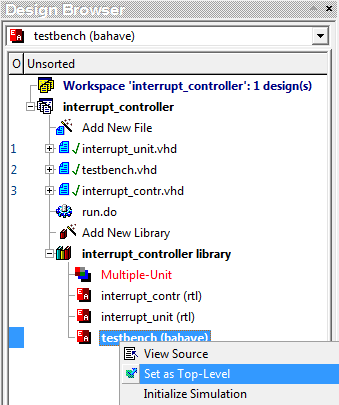

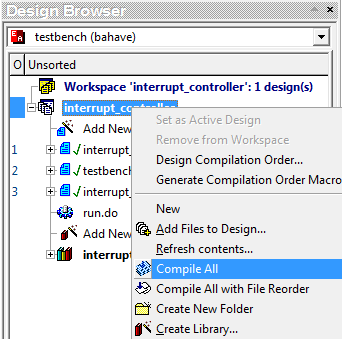

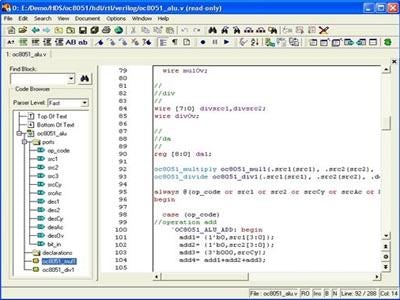

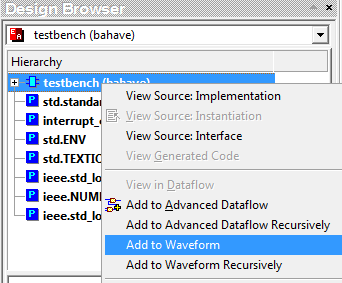

The blocks field lists all of the available blocks within the design. Only after this can we move on to the next step in the chip design workflow. Active hdl gui design settings. Also conversion of myhdl testbench to hdl testbench is discussed.

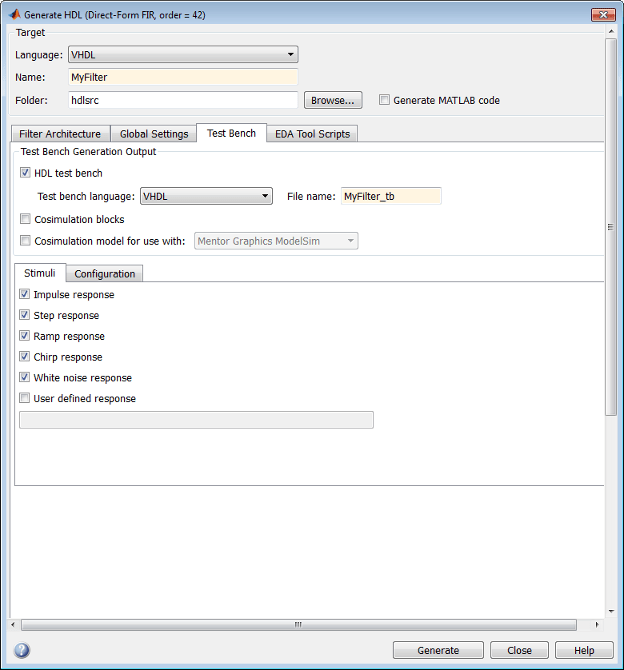

A test bench is hdl code that allows you to provide a documented repeatable set of stimuli that is portable across different simulators. Testbench provide stimulus for design under test dut or unit under test uut to check the output result. Submit your solution in pdf format. O the fixed point optimization script for data type optimization.

Testbench in this chapter we write the testbench for the listing 2 1. Design 2 1 mux verilog hardware description language along with testbench. O the project folders generated by the hdl workflow advisor containing the generated hdl codes hdl test benches and all synthesis results. A lot of people wonder about the difference between rtl and hdl.